次世代エレクトロニクス向け自己組織化ナノ誘電体(SAND)

はじめに

従来にない新規エレクトロニクス技術によって、既存の半導体およびエレクトロニクス分野に新たな産業がもたらされることが期待されています1-9。対象とする分野は広く、「プリンテッド有機/無機」エレクトロニクスと「透明」エレクトロニクスの両方を含んでいます。1つ目の技術は、RF-IDタグ、「スマート」カード、フレキシブル電子ペーパー、アクティブマトリックスディスプレイ向けバックプレーン回路などの極めて安価な電子デバイスを高スループットで製造することを目指しています。2つ目の技術は、透明な回路やモニターなどの「見えない」デバイスを対象にしています。現在利用されているどのエレクトロニクス技術においても、主要なコンポーネントは薄膜トランジスタ(TFT:thin-film transistor、構造と機能については図1参照)であり、TFT材料の3つの基本コンポーネントは、電極(ソース、ドレイン、ゲート)、半導体、およびゲート誘電体です。

図1薄膜トランジスタの構造と動作原理についての模式図。飽和状態でのTFTドレイン電流を記述する基本方程式は、ISD = (W/2L) μCi (VSG-VT)2(式1)です。ここで、μ は半導体の電界効果キャリア移動度、Wはチャネル幅、Lはチャネル長、Ciは誘電体層の単位面積あたりの静電容量、VTはしきい値電圧、VSDはドレイン電圧、VGはゲート電圧です。従来型のSiトランジスタとは対照的に、通常、有機TFTは蓄積(accumulation)モードで動作します。このモードでは、ゲート電圧を印加するとチャネル中に移動性電荷キャリアが生成されて、デバイスのスイッチが「オン」になります。半導体の電界効果移動度は、式1に従ってI-Vデータから求められます。デバイス電流、Ion:Ioff比、およびサブスレッショルド係数(subthreshold slope、サブしきい値係数、S値。ゲート電極による素子のオンオフ抵抗比であり、ドレイン電流を1桁変化させるのに必要なゲート電圧で、デバイスがオンになる速度に関連)も重要なTFTの性能特性です。

これまでの研究では高い移動度と安定性を持ち、場合によっては印刷可能な透明半導体の探索に重点が置かれていましたが、現在、デバイス性能を最適化するために適切なゲート誘電体を使用する必要があることがはっきりしています。自己組織化ナノ誘電体(SAND:self-assembled nanodielectrics)は、高い絶縁特性、ナノメートルレベルで調節可能な膜厚、可視領域での光学的透明性、および効率的な溶液処理特性を持つことから、ゲート誘電体として大きな注目を集めています。本論文では、基本的なSANDの構造、機能、および各種半導体との組み合わせによるTFTの作製10についてまとめます。

SANDの化学、作製、および特性

従来の有機/透明TFTは、ゲート誘電体として100~300 nmの厚さのSiO2絶縁層を使用して製造されています11。この物質によって、ソース/ドレイン間のチャネル領域とゲート間の漏れ電流を防ぎ、半導体層が正確な電気的性能特性を発揮することが可能になります。SiO2に替わるゲート誘電体の探索は、低コストでTFTを製造し、かつ駆動電圧を大幅に引き下げることを目標に進められています。駆動電圧の低下はつまり、消費電力が低減することでバッテリーによる携帯型電子機器の動作時間が長くなることを意味します。式1(図1の説明文)によれば、低バイアスで駆動させたときのTFTのソース-ドレイン電流(ISD)を大幅に増加させるには、ゲート誘電体の静電容量Ci = ε0(k/d)を増加させることが必要です。ここで、kは材料の誘電定数、dは絶縁体の厚さです。重要な点は、SANDなどの代替TFTゲート誘電体は、大きな静電容量をもつだけでなく、ゲート漏れ電流が一定の許容範囲(ISDの1%未満)でなければならないことです。SAND誘電体は一種の自己組織化多層膜であり、固体表面への活性分子前駆体の自発的な吸着によって形成される、規則性をもった分子集合体で構成されています。通常、前駆体の分子種は、一般的な有機溶媒から溶液プロセスにより段階的に積層されます。SANDの作製の場合、有機シラン分子(Alk、Stb、およびCap、図2参照)が使用されます。この自己組織化反応にはヒドロキシル化処理した基板表面が必要で、基板にはSiO2、Al2O3およびITO表面などが用いられます。自己組織化の推進力はシロキサン結合のin-situ 形成であり、これによって、前駆体シラン化合物が強固な共役-Si-O-結合を介して表面水酸基(-OH)と結合します。現在、SANDは図2のように分子層を繰り返し積層することで作製されます。(a)α,ω-二官能性炭化水素鎖[Cl3Si(CH2)nSiCl3](Alk)の自己組織化二官能性炭化水素の単分子層の各分子が、隣接する分子と架橋することで高精度の段階的な積層が可能になり、鎖間の充填度が向上して欠陥やピンホールが少なくなります。(b)高分極性「push-pull」スチルバゾリウム(stilbazolium)層(Stb)自己組織化した配向性π電子双極子層は、デバイスがオンになった時(VG ≠ 0)に隣接する半導体チャネル中の電荷キャリアを安定化させます。(c)オクタクロロトリシロキサンキャッピング層(Cap)高度に架橋したガラス状構造のシロキサン高分子を使用したキャッピング/平面化によって、多層構造をさらに強固にすることができます。

図2左:高濃度ドープしたSi(100)、Al、またはITO基板/ゲート電極上にタイプIIIの自己組織化ナノ誘電体(SAND)構造(右)が作製された、薄膜トランジスタ(TFT)コンポーネントの概念図。ナノ誘電体層(タイプIIIのSAND構造では厚さ5.5 nm)はステップi.~iv.の手順に従って、シラン前駆体Alk、Stb、Cap(左)を層ごとに溶液から積層させます。OTFTデバイスの作製は、半導体化合物(ステップv.)と最後のソース-ドレイン電極(ステップvi.)の蒸着により完成します。右:SANDに使用される、いくつかのp型(青)およびn型(赤)有機半導体の構造式と、SANDベースのTFT製造に使用されるその他の半導体化合物。

前駆体のさまざまな組み合わせによって、多様な種類のSAND多層構造を作製(および測定)することができます。最も一般的なSAND構造は、Alk+Cap層(タイプI)、Stb+Cap層(タイプII)、およびAlk+Cap+Stb+Cap層(タイプIII)に分類されます。有機半導体を用いたTFTの製造に最もよく使用されるSANDはタイプIII(厚さ約5.5 nm)ですが、無機半導体ベースのTFTに最もよく使用されるのは、タイプIIIの3層構造(タイプIII x 3、厚さ約16 nm)です。SANDのミクロ構造と電気特性は、X線反射率測定、光吸収分光法、光第2高調波測定法、原子間力顕微鏡、および走査電子顕微鏡によって解析されます。SANDは、サイクリックボルタンメトリーとMIS漏れ電流測定(電流密度:約10-8~10-5 A/cm2)によってピンホールのない優れた絶縁体であることが確認されており、測定された絶縁耐圧は約5~7 MV cm-1でした。MIS構造での静電容量-電圧(C-V)測定(図3)では、102 Hzでの最大静電容量がCi = 400(タイプI)、710(II)、390(III)、約180(III x 3)nF cm-2を示しました(絶縁層が膜厚300 nmのSiO2では約11 nF cm-2)。

図3102~105 Hzの間における蓄積モード(1.0V)での各SANDナノ誘電体の静電容量の周波数(f)依存性

このように、TFT駆動電圧を大幅に低下させることが可能です。また近年、タイプI~IIIを120~180℃でアニールすると、C-Vヒステリシスの幅とC-V特性の周波数分散性が低下することが分かりました。さらに、SANDタイプIII x 3薄膜は熱安定性が高く、400℃でアニールすると誘電強度の向上や漏れ電流の低減、および静電容量の増加が見られるため、高温処理の必要な無機半導体との集積という、これまでにないデバイス作製の可能性が広がると考えられます。

有機半導体-SANDトランジスタ

第1世代のSANDを用いた有機TFTは、ノースウェスタン大学とPolyera社によって見出され・開発された各種有機半導体を使用して、ドープされたシリコン基板(ゲート)上に作製されました13,14。初期の研究では、デバイスは半導体層を蒸着またはスピンコーティングによって堆積した後、ソース/ドレインをAu蒸着することで作製しました。しかし、Polyera社での最近の研究では、SAND上への半導体化合物のインクジェット印刷が可能であることが確認されています。用いた半導体は、各種ペンタセン、オリゴチオフェン、ポリチオフェン、金属フタロシアニン、ペリレンなどです。SAND-有機半導体ベースのデバイスはすべて、極めて低いバイアスで典型的な線形特性と飽和応答特性を持つ、再現性の高いI-V特性を示します。図4に、代表的なp型(Polyera ActivInk P0300)とn型(Polyera ActivInk N1200)の有機半導体を用いた場合のデータを示します。

図4pチャネル(ActivInk P0300)とnチャネル(ActivInk N1200)有機半導体を用いたSANDベース有機トランジスタの、異なるゲート電圧(VG)での出力特性

これらの結果とはまったく対照的に、一般的に用いられているSiO2誘電体(厚さ:300 nm、Ci:約11 nF/cm2)で作製された比較対照用のデバイスは、同じ電圧範囲内で実用的なソース-ドレイン電流変調を示しません。これらの有機半導体のキャリア移動度はSi-SiO2基板上で得られた値と同程度であり、ActivInk P0300とActivInk N1200のいずれでも約0.1 cm2/Vsです。一方、ITOコートしたガラス基板のゲート上に作製されたTFTでもまた同程度に機能するため、優れた誘電性能を得るのにSi/SiO2酸化物ゲート電極が必要ないことは注目に値します。なお、これらのナノ誘電体は、商用化されているITOコートしたプラスチック(Mylar)へのフレキシブルTFTの製造にも用いることができます。ナノ誘電体のフレキシブルプラスチックエレクトロニクスへの応用の可能性が期待されます。

無機半導体-SANDトランジスタと回路

我々は次に、低分子有機化合物以外の半導体とSANDとの適合性を詳細に調べました。最初に、タイプIII x 3のSANDと半導体として単層カーボンナノチューブ(SWCNT:single-wall carbon nanotube)を用いた場合の親和性を確認しました15。SWCNTは、SiO2/Siウエハ上にCVDにより成長させ、Si-SAND基板上(および、比較対照用Si/SiO2基板上)に直接転写印刷しました(約10 tubes/μm2)。SWCNT-SAND間は接着性が高いため、リフトオフによる直接フォトリソグラフィーでソースおよびドレイン電極をパターニングできます。こうして作製したTFTでは、ヒステリシスとVTシフトが大幅に減少し、100 nm Si/SiO2ゲート誘電体を使用した従来型デバイスと比較してTFT性能が大幅に改善され、μhole = 約5.6 cm2/Vs、VT = 0.2Vという優れたTFT移動度と、VG = -1Vで約10 nAという低いゲート漏れ電流が確認されました。さらに、(ポリエチレンイミンで被覆した)n型SWCNTとの親和性も確認され、低ヒステリシス性とμelectron = 4.1 cm2/Vs、VT = -2VのTFT特性が観測されています。一方、薄膜無機半導体とSAND誘電体との親和性は、In2O3薄膜を使用して明らかなため、高性能、低電圧、かつ完全に透明なTFTを実現することができます8。In2O3は可視領域で非常に優れた透過性(>90%)を持つ、ワイドバンドギャップ(3.6~3.75 eV)n型半導体です。デバイスは、In2O3薄膜をイオンアシスト蒸着法(IAD:ion-assisted deposition)により室温でSAND誘電体上に直接蒸着し、ソース/ドレインをAu蒸着することにより作製しました。SANDが、In2O3の蒸着中にin-situ のイオン/プラズマ照射に対して安定であったことは注目に値します。こうして作製したSANDをゲートとしたIn2O3-TFTにおいて大幅な性能向上が見られ、μ = 140 cm2/Vs、界面トラップ密度D = 1011 cm-2、VT = 0.0V(ヒステリシス特性をほとんど示さない)、オン/オフ比 = 105、サブスレッショルド係数 = 150 mV/decadeが得られています。これらの数値は、比較対照のために作製した従来のSi/SiO2のゲートを持つデバイスの性能(μ = 10 cm2/Vs、オン/オフ = 105)と比較して優れた値です。さらに、完全に透明なTFTを作製するために、ボトムゲート電極としてガラス/ITOを使用しIn2O3のソースおよびドレイン電極を使用した以外は、前述と同じ方法を用いてデバイスを作製しました。このSANDベースの透明TFTの性能は、n+-Si基板を用いた場合と本質的に同じですが、サブスレッショルド係数が90 mV/decadeに改善しています。

有機化合物以外の半導体と共に用いられる有用なゲート誘電体としてのSANDの多様性は、ZnO、In2O3、およびSnOナノワイヤー(NW:NanoWire)を使用したTFTで詳しい検証がなされています17,22。たとえば、ZnO NW(平均直径80 nm、平均長さ5 μm)を2-プロパノール中に分散させ、SANDコートした基板に転写することで、ゲート誘電体としてSANDIII x 3を使用したZnO NW-TFTを作製しました。ソースおよびドレインAl電極は電子ビーム蒸着法により蒸着し、フォトリソグラフィーでパターン形成しました。SAND誘電体について、まずMISデバイス(Al/SAND/Si)における電気的特性が測定され、約10-8 A/cm2の漏れ電流密度が観測されました。このように、SANDはフォトリソグラフィーおよび電子ビーム蒸着法との親和性が高いことがわかります。さらに、SANDをゲートとして持つZnO NW-TFTでは、デバイスオン/オフ比を保ったまま、オン電流が0.3 μAから2 μAに増加し、さらに移動度と相互コンダクタンスも増加させながら、駆動電圧は1.5V未満に低下しています(Si/SiO2では1.5V以上)。SANDゲートを持つZnO NW-TFTのVTは-0.4V、サブスレッショルド係数は400 mV/decadeです。サブスレッショルド係数が大きい要因は一般的に表面のトラップが原因であるため、SANDベースのZnO NW-TFTをオゾン照射処理したところ、実際にサブスレッショルド係数は150 mV/decadeに低下しました。さらに、VT値の低下(0.2V)とオン/オフ比の改善(108)も見られました。計算により求めた(筒状のチャネル形状であることを考慮した)電子移動度は196 cm2/Vsですが、これは、膜厚のあるSi/SiO2誘電体上のZnO NWで測定された8~18 cm2/Vsや、比較用に作製した厚さ70 nmのSiO2誘電体での54 cm2/Vsをはるかに超えています。TFT移動度は、NWの直径と長さの変化に応じて、164~181 cm2/Vsの間で変動します。SANDを用いたエレクトロニクスに顕著な特性の1つは、耐放射線性として知られる放射線損傷に対する耐性です。最初に、SANDIII x 3/ZnO-NW TFTのプロトン(10 MeV H+)放射線耐性が検証されました18。原子炉中でさまざまな照射および暴露条件に置いた後でも、SANDゲートを持つTFTの漏れ電流とVTがいずれも大幅にシフトすることはありませんでした。現在、SANDゲートを持つ有機および無機TFTは、追加の放射線試験のために国際宇宙ステーションに搭載されています。これらの結果が意味することは、H+照射中に形成されるバルク酸化物トラップ密度とSAND(SAND-ZnO NW界面)の界面トラップ密度は、同様に照射した従来型のSiO2ゲート誘電体での密度よりはるかに小さいということです。一方、低周波ノイズとI-Vの温度依存性測定を用いたZnO NW-TFTの詳細な研究によって、表面/界面状態の特性が明らかになっています23。SANDを用いたデバイスは、SiO2ベースのデバイスより1/f ノイズ定数が低く、さらにHooge定数の比較により、界面トラップ密度は先に述べたSWCNTデバイス(D=約1012 cm2V-1)の場合と同程度であると考えられます。SiO2/ZnO-NW TFTに見られる伝達特性の温度変化や温度に対するしきい値電圧シフトが、対応するSANDゲートを持つデバイスより大きいことで、SAND/ZnO-NW TFTが例外的に低い界面トラップと欠陥密度を持つことのさらなる裏づけとなります。

上述したすべての実験結果は、SANDが多くの無機半導体と親和性を持つ堅牢性の高いゲート誘電体であることを示しています。しかし、これらの半導体化合物の蒸着はすべて室温近くで行われたため、SANDはより高い温度でも安定しているのかという疑問が残ります。ごく最近、我々はSANDIII x 3膜が400℃で安定であることを実証し、高温での加工処理の可能性を示しました19。具体的には、水溶液における湿式処理で調製した無機半導体と有機誘電体材料を組み合わせてTFTを作製するというもので、溶液プロセスで調製したセレン化カドミウム(CdSe)、In2O3、およびITOを半導体層として用いた場合の、SANDベースのTFTとの親和性を検証しました。一例として、化学浴析出法(CBD:chemical bath deposition)によってSANDIII x 3ゲート誘電体層上にCdSe膜を蒸着しました。400℃でアニールしたCdSe/SANDベースのTFTにて最適な条件で作製した場合に、オン/オフ比 = 106、VT = 3.0V、およびサブスレッショルド係数 = 0.26 V/decadeを達成し、移動度は、同等の構造のSiO2ベースのデバイスが約4 cm2/Vsであるのに対して、約40 cm2/Vsを示しました。TFT半導体として酸化インジウム(In2O3)20とITOを使用した場合にも、同様に優れた性能が得られました。

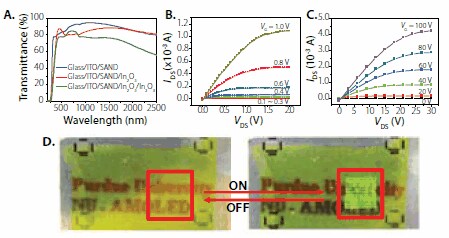

最後の例として、我々はSAND/ナノワイヤーの概念を利用して、ZnOやIn2O3のナノワイヤーおよびITOまたはAZO(Al-Zn-O)のソース/ドレイン/ゲートを用いた、完全に透明な回路を作製しました24。この回路を基に、室温で作製したナノワイヤートランジスタ(NWT:nanowire transistor)エレクトロニクスのみで構成されたスイッチング回路および駆動回路を利用して、アクティブマトリックス有機EL(AMOLED:active matrix organic light-emitting diode)ディスプレイの作製21を試みました(図5)。このSANDベースのIn2O3 NW-TFTの移動度は約160 cm2/Vsであり、高輝度の画素を駆動するには十分な値です。こうして、完全に透明なデモンストレーション用の2 x 2 mm NW-AMOLEDアレイ(300ピクセル = 900 NWT)が、ガラス基板上の超薄膜Alカソードを使用して作製されました20。350~1350 nmの波長領域での光学透過率は約72%(OLED蒸着前)および約35%(OLED蒸着後。より薄いAl薄膜が必要)であり、300 cd/m2を超える緑色をピークに持つ発光を示しました。これまでに、プラスチック基板上のOLED構造では最大で70%の透過係数が報告されていますが、50%程度の値が一般的であることに注意してください。

図5A. SANDゲート誘電体とIn2O3薄膜を用いた透明TFTの作製に使用された多層膜の光学透過率。B.、C. イオンアシスト蒸着法によるIn2O3薄膜とSAND(B)、およびSiO2(C)のトランジスタ出力特性。駆動電圧の差異に注目。D. ナノワイヤーエレクロニクスに基づく、半透明アクティブマトリックス有機LEDディスプレイ(次ページにて説明)21。

結論

本稿では、有機、無機、透明TFTのほか、TFT回路や有機ELディスプレイに利用される、シラン前駆体から製造された自己組織化多層ゲート誘電膜の可能性と展望を簡単にまとめました。これらの優れたSANDの成果は、独創的かつ有用な電子材料を構築する上で分子化学の持つ可能性の大きさを見事に表しています。

謝辞

本研究に対するNR(N00014-05-1-0766)、AFOSR(FA9550-08-1-0331)、Polyera社の支援、およびノースウェスタン大学 材料研究科学工学センターを通じたNSF-MRSECプログラム(DMR-0520513)の支援と分析設備の提供に感謝いたします。また、本研究に関わったすべての方々の多大な貢献に深く感謝いたします。

参考文献

続きを確認するには、ログインするか、新規登録が必要です。

アカウントをお持ちではありませんか?